CMOS implementation of XOR, XNOR, and TG gates

Nov 3, 2021 · Learn how to implement the logic gates XOR, XNOR, and Transmission Gate (TG) using CMOS. The CMOS family is the top choice for digital-logic design due to its many advantages. This article shows some logic gates implemented with CMOS. In an XOR circuit, the output is a logic 1 when one and only one input is a logic 1.

Lab6 - Designing NAND, NOR, and XOR gates for use to design …

Oct 13, 2013 · Design, layout, and simulations of CMOS NAND, NOR, XOR gates and a full-adder. Authored by Adam James Wolverton. Email: [email protected]. Today's Date: 10/13/2013. Lab description: 1) Go through the video tutorial 4 and learn how to design schematic/layout for NAND and NOR gates.

Designing CMOS Logic: XOR, XNOR, and Transmission Gates

The XOR, XNOR, and Transmission Gates, designed using CMOS technology, are valuable in digital electronics. The XOR gate, used in error detection and arithmetic, and the XNOR gate, needed for equality comparisons, demonstrate CMOS technology's efficiency in creating reliable, low-power circuits.

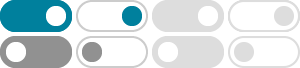

• NMOS and PMOS connected in parallel • Allows full rail transition – ratioless logic • Equivalent resistance relatively constant during transition • Complementary signals required for gates • Some gates can be efficiently implemented using transmission gate logic (XOR in particular) ==

nmos - Why do we need transmission gate for XOR (transistor …

May 22, 2022 · The 4-transistors circuit behaves like a bad XOR gate. When A=0, the second NMOS/PMOS acts like a bad buffer, for B = VDD => Y = VDD - Vthn, for B=0 => Y=Vthp (the capacitances at node Y will never fully charged/discharge to VDD or 0).

CMOS Logic Gate - GeeksforGeeks

Jun 6, 2024 · The XOR or Exclusive OR Gate is a special type of logic gate used in digital electronics to perform the exclusive OR operation. The XOR gate takes two inputs and produces an output depending on the combination of the two inputs applied.

In this lab, you will design two different XOR layouts using Cadence as shown in Fig 1. And after parameter extraction, you'll simulate the netlist using AimSpice. For simplicity, assume the complimentary signals are given as shown in Fig.1. Make sure …

Pseudo-NMOS XOR Gate An example of XOR gate realized with pseudo-NMOS logic The XOR is defined by Y =X 1 ⊕X 2 =X 1 X 2 +X 1 X 2 =X 1 X 2 +X 1 X 2 =X 1 X 2 +X 1 +X 2 Y X 1 X 2 Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 5

Lab 6 - CMOSedu.com

We will begin with a NAND gate, followed by NOR and XOR. A schematic, icon and layout will be created for each gate, and a simulation showing proper operation will be performed for each. Lastly we will create full adders using our CMOS gates.

XOR-gate-using-pass-transistor-logic | Digital-CMOS-Design ...

'XOR' gate using pass transistor logic. The truth table of 'XOR' gate is as shown in Table below. Figure below shows the implementation of 'XOR' function using pass transistors. In this gate if the B input is low then left NMOS transistor is ON and the logic value of A is copied to the output F.