Using Deep N Wells in Analog Design - CSDN博客

Oct 19, 2021 · Connection to the deep N well is formed by a N well ring that is connected to VDD. The deep N well has the effect of decreasing the noise coupling through it to the substrate and giving the advantage of fully isolated NMOS devices – which can in theory be at a different potential from ground.

NMOS transistor layout with a deep N-well - ResearchGate

In this paper, a self-biased temperature-compensated CMOS voltage reference operating at picowatt-level power consumption is presented. The core of the proposed circuit is the self-cascode MOSFET...

VCO is an Oscillator of which frequency can be Controlled by external Voltage stimulus. One of major applications for VCO is a frequency synthesizer. Frequency synthesizer provides sinusoidal/pulse signals at predetermined frequencies that is …

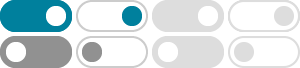

Layout and DFM | KNOW-HOW - raytroop.github.io

Nov 19, 2022 · This technique was used to layout current mirrors and resistors in PTAT and BGR circuits. In the Figure-15 below each brown stick represents a PFET of uniform length. This representation is termed as an inter-digitated layout.

DNW MAPS are evolving towards vertical integration. robust against background. Binary readout: ILC VTX demands a pixel pitch < 20 μm to achieve required single point resolution < 5 μm.

Cross section of a Deep N-Well Process. - ResearchGate

DNW process architecture is shown in Fig. 1. The Deep N-Well layer is connected to the n-well and creates two vertical PN junctions: one with the formed isolated p-type region in the surface...

Compared with the design using a standard inductor, the proposed deep N-well (DNW) and patterned ground shield (PGS) VCOs demonstrated clearly reduced third-order intermodulation spurs by 6–8 and 10–15 dB, respectively.

The MOS varactor is formed by thin gate-oxide over Nwell, with N+ implants at both ends of the NWELL to form ohmic contacts with the varactor Nwell region. The cross section of this device is shown in Figure. The equivalent circuit of the device is shown in FIGURE 2.0 generated for use in high frequency circuits. * Vgb = gate to nwell voltage.

Shared deep N well devices in UMC 65nm - Forum for Electronics

Jan 20, 2011 · As an example I have a simple two stage inverter layout. Here is each inverter spaced out so there's no overlap between the cells. The white hollow polygon is the nwell (NWEL). It has a void in the middle, for some reason. The inner reddish rectangle is the deep nwell (DNW). This is as close as I can get them before DRC errors kick in.

• Accurate dC/dV critical for VCO phase noise – Accurate models for device resistance over geometry • Combined with C yields accurate quality factor (Q) key to VCO phase

- Some results have been removed