Examples of VHDL Conversions - Nandland

Examples of all common VHDL Conversions. Convert from std_logic_vector to integer in VHDL. Includes both numeric_std and std_logic_arith.

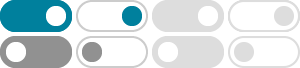

VHDL Type Conversion - BitWeenie

Feb 10, 2013 · VHDL Type Cast and Conversion Functions. The picture below illustrates how to convert between the most common VHDL types. Type casting is used to move between the …

An Introduction to VHDL Data Types - FPGA Tutorial

May 10, 2020 · The first method is to simply cast the signal to the correct type. We can use this method to convert between the signed, unsigned and std_logic_vector VHDL data types. The …

VHDL: Converting from an INTEGER type to a STD_LOGIC_VECTOR

You can convert a std_logic_vector to an integer, but you'll have to cast it as signed or unsigned first (as the compiler has no idea which you mean). VHDL is a strongly typed language. I've …

Common Conversions in VHDL Programming Language

In this post, I’ll introduce you to common conversions in VHDL, explain their importance, and provide examples of how to use them in your designs. By the end, you’ll have a solid …

VHDL typecast signed to std_logic_vector - Stack Overflow

Sep 23, 2017 · As VHDL is a strongly typed language, you cannot just put the data from one type to another. You need to use type conversion. For unrelated types, you should implement a …

Where are VHDL type cast functions defined?

In VHDL one can cast one type to another using the name of the other type e.g signal x : std_logic_vector(7 downto 0); signal y : signed(7 downto 0); ... y <= signed(x) Here we use the …

How to typecast integer to unsigned in VHDL - Stack Overflow

Aug 28, 2013 · If you want to pass integers as unsigned vectors, you need to convert them, not typecast them. First you want the numeric_std library:

vhdl - Integer to real conversion function - Stack Overflow

Aug 6, 2014 · Is there a common conversion function to convert a integer type object to a real type in VHDL? This is for a testbench so synthesizability is a non-issue.

VHDL Type Conversion? - Hardware Coder

Feb 25, 2020 · VHDL type conversion is called casting. It's done by writing the type we want to cast to followed by the object we want to cast in parentheses. Example : signal a : …